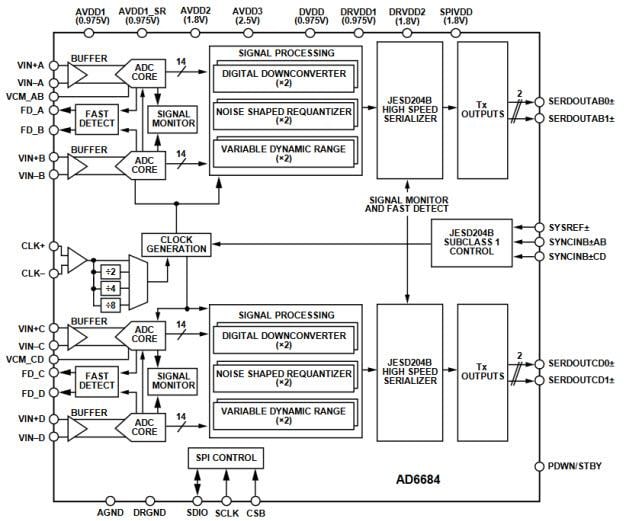

クワッドADCコアは、出力誤差補正ロジックを内蔵する多段の差動パイプライン・アーキテクチャを採用しています。各ADCは、選択可能な様々な入力範囲をサポートする広帯域入力を備えています。SPIプログラマブルプロファイルを使用して、AD6684レシーバをDDC、NSR、VDRモードで実行できます。ADCの各データ出力ペアは、クロスバー・マルチプレクサを介して2個のDDC に内部で接続されています。各DDCは、最大5つのカスケード接続された信号処理段(48ビット周波数変換器、NCO、最大4個のハーフバンド・デシメーション・フィルタ)で構成されています。ADC出力はNSRブロックに接続されています。AD6684の内蔵のNSR回路は、ナイキスト帯域内のより小さな周波数バンドでのSNR性能を向上させ、9ビットの出力分解能を維持します。

さらに、IFレシーバの各出力ペアは、JESD204B(サブクラス1)ベースの高速シリアル出力の1本または2本のレーンに設定することができます。SYSREF±、SYNCINB±AB、SYNCINB±CD入力ピンにより、複数デバイスの同期に対応します。

AD6684のオンチップ・バッファとサンプル・アンド・ホールド回路によって、低消費電力動作、小型サイズ、使い勝手の良さが実現します。AD6684 135MHzクワッドIFレシーバの全体的な設計は、最大1.4GHzのアナログ信号をサンプリングする通信アプリケーションに最適です。

特徴

- JESD204B(サブクラス1)コードのシリアル・デジタル出力レーン・レート最高15Gbps

- アナログ・デジタル・コンバータ(ADC)チャンネルあたり500MSPS420mWでの総電力1.68W

- 305MHzでのSFDR = 82dBFS(1.8Vp-pの入力範囲)

- 305MHzでのSNR = 66.8dBFS(1.8Vp-pの入力範囲)

- ノイズ密度 = −151.5dBFS/Hz(1.8Vp-pの入力範囲)

- アナログ入力バッファ

- 小信号の線形性を改善するためのオンチップディザリング

- 柔軟性に富んだ差動入力範囲1.44Vp-p~2.16Vp-p(公称1.80Vp-p)

- 82dBのチャンネル・アイソレーション/クロストーク

- 0.975V、1.8V、2.5VのDC電源動作

- メイン・レシーバ用ノイズシェーピング再量子化器(NSR)オプション

- デジタル・プリディストーション(DPD)用可変ダイナミック・レンジ(VDR)オプション

- 4つの統合ワイドバンド・4デジタル・ダウンコンバータ (DDC) 48ビット数値制御発振器(NCO)、最大4個のカスケード接続ハーフバンド・フィルタ

- 1.4GHzのアナログ入力フルパワー帯域幅

- 自動ゲイン制御(AGC)を行うのに効率的な振幅検出ビット

- 差動クロック入力

- 1、2、4、または8の整数クロック分周比

- 温度ダイオードを内蔵

- 柔軟なJESD204Bレーン構成

アプリケーション

- 通信

- ダイバーシティマルチバンド、マルチモードのデジタルレシーバ

- 3G/4G、W-CDMA、GSM、LTE、LTE-A

- HFCデジタルリバースパスレシーバ

- デジタル・プリディストーション監視パス

- 汎用ソフトウェア無線

機能ブロック図

公開: 2017-07-31

| 更新済み: 2022-04-18