GOWIN LittleBee® GW1N-1S FPGAs

GOWIN Semiconductor LittleBee® GW1N-1S FPGAs provide many logic resources, multiple I/O standards, embedded BSRAM, DSP, PLL, and built-in flash. The non-volatile FPGAs have many desirable options, including low power, instant start, low cost, high security, a small size, a variety of packages, and flexible usage.The GOWIN Semiconductor GW1N-1S FPGAs are part of the LittleBee family of devices. LittleBee products are based on 55nm LP technology and offer instant-on, non-volatile, low-power, intensive I/O and a small footprint (the smallest is 2.4mm x 2.3mm). The LittleBee family is ideal for high-performance bridging applications and supports MIPI I3C and MIPI D-PHY as standard. This further reduces the board space and enhances performance.

The GW1N-1S apply FPGA synthesizing, layout, place and routing, data bitstream generation, and downloads through GOWIN Semi's FPGA hardware development environment.

Features

- User Flash

- 100,000 write cycles

- Greater than 10 years of data retention at +85℃

- Selectable 8/16/32 bits data-in and data-out

- 256 bytes Page size

- 3μA standby current

- 8.2ms Page write time

- Lower power consumption

- 55nm embedded flash technology

- LV - Supports 1.2V core voltage

- Clock dynamically turns on and off

- Multiple I/O standards

- LVCMOS33/25/18/15/12; LVTTL33, SSTL33/25/18 I, SSTL33/25/18 II, SSTL15; HSTL18 I, HSTL18 II, HSTL15 I; PCI, LVDS25, RSDS,

- LVDS25E, BLVDSE, MLVDSE, LVPECLE, RSDSE

- Input hysteresis option

- Supports 4mA, 8mA, 16mA, 24mA, etc. drive options

- Slew rate option

- Output drive strength option

- Individual Bus Keeper, Weak Pull-up, Weak Pull-down, and Open Drain option

- Hot socket

- High-performance DSP

- High-performance digital signal processing ability

- Supports 9 x 9, 18 x 18, 36 x 36bit multiplier and 54bit accumulator

- Multipliers cascading

- Registers pipeline and bypass

- Adaptive filtering through signal feedback

- Supports barrel shifter

- Abundant slices

- 4 input LUT (LUT4)

- Double-edge flip-flops

- Supports shift register and distributed register

- Block SRAM with multiple modes

- Supports dual port, single port, and semi-dual port

- Supports bytes write enable

- Flexible PLLs

- Frequency adjustment (multiply and division) and phase adjustment

- Supports global clock

- Built-in flash programming

- Instant-on

- Supports security bit operation

- Supports AUTO BOOT and DUAL BOOT

- Configuration

- JTAG configuration

- Up to 6 GowinCONFIG configuration modes - AUTOBOOT, SSPI, MSPI, CPU, SERIAL, DUAL BOOT

Applications

- Embedded

- Server

Additional Resources

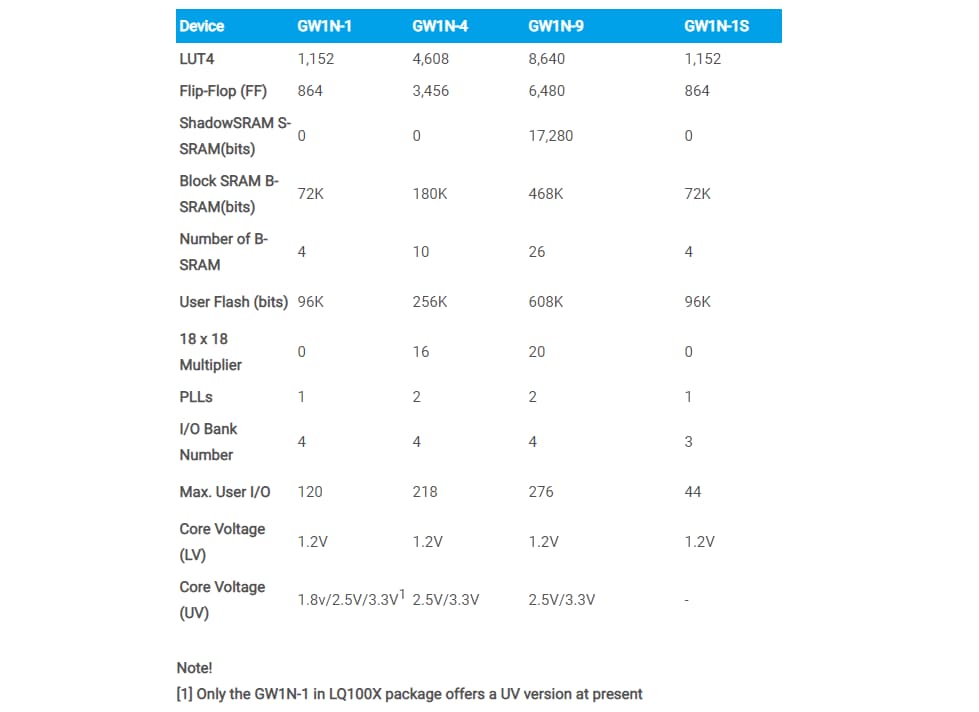

Specifications Chart

Pinout

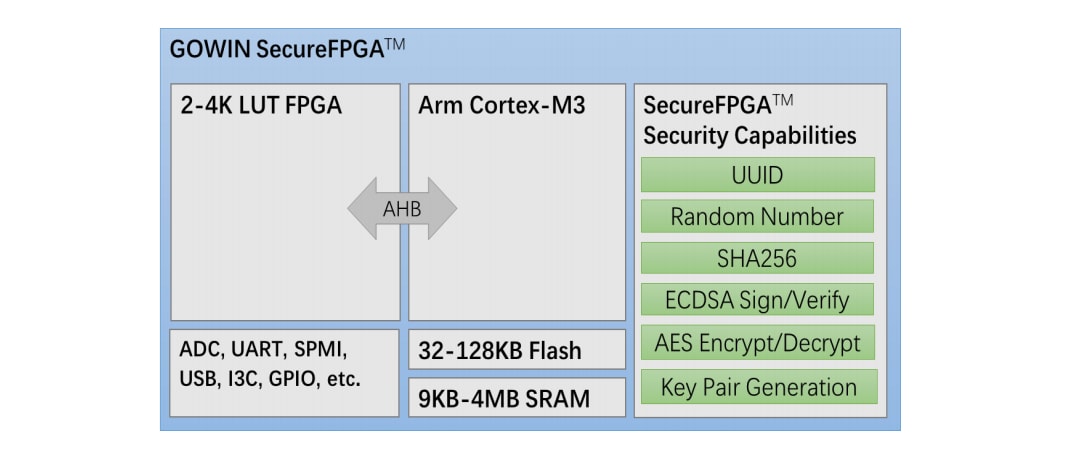

SecureFPGA Device Diagram

公開: 2020-07-16

| 更新済み: 2024-09-06