GOWIN LittleBee® GW1NZ-1 FPGAs

GOWIN Semiconductor LittleBee® GW1NZ-1 FPGAs provide an Always On, ultra-low power consumption at extremely low costs. The GW1NZ-1 FPGAs feature ultra-low power consumption, instant on, low cost, non-volatile, high security, various packages, and flexible usage. The non-volatile GW1NZ-1 FPGAs enable flexible usage with various packages.The GOWIN Semiconductor GW1NZ-1 FPGAs are part of the LittleBee family of devices. LittleBee products are based on 55nm LP technology and offer instant-on, non-volatile, low-power, intensive I/O and a small footprint (the smallest is 2.4mm x 2.3mm). The LittleBee family is ideal for high-performance bridging applications and supports MIPI I3C and MIPI D-PHY as standard. This further reduces the board space and enhances performance.

The GW1NZ-1 FPGAs are widely used in communication, industrial control, and consumer (especially mobile and wearable) applications.

Features

- Ultra-low power consumption

- 55nm embedded flash technology

- LV - Supports 1.2V core voltage

- ZV - Supports 0.9V core voltage (below 28uW power consumption Always On)

- Power management module

- Clock dynamically turns on and off

- User Flash dynamically turns on and off

- Power Management Module

- SPMI - System power management interface hard core

- VCC and VCCM are independent in the device

- User Flash

- Dynamically turns on and off

- 64K bits

- 32 Data width

- 10,000 write cycles

- Greater than ten years' data retention at +85℃

- 2048bytes per page support page erasure

- Max. 25ns duration

- Electric current

- 2.19mA/25ns (VCC) & 0.5mA/25ns (VCCX) (MAX) Read operation

- 12/12mA (MAX) Write operation/erase operation

- Quick page erasure/Write operation

- 40MHz Clock frequency

- ≤16μs Write operation time

- ≤120ms Page erasure time

- Multiple I/O Standards

- LVCMOS33/25/18/15/12 LVTTL33, PCI

- LVDS25E, BLVDSE, MLVDSE, LVPECLE, RSDSE

- Input hysteresis option

- Supports 4mA, 8mA, 16mA, 24mA, etc. drive options

- Slew rate option

- Output drive strength option

- Individual Bus Keeper, Weak Pull-up, Weak Pull-down, and Open Drain option

- Hot socket

- I3C hardcore, supports SDR mode

- Support differential output rather than differential input

- Abundant slices

- Four input LUT (LUT4)

- Double-edge flip-flops

- Supports shifter register

- Supports shadow SRAM

- Block SRAM with multiple modes

- Supports Dual Port, Single Port, and Semi Dual Port

- Supports bytes write enable

- Flexible PLLs

- Frequency adjustment (multiply and division) and phase adjustment

- Supports global clock

- Built-in flash programming

- Instant-on

- Supports security bit operation

- Supports AUTO BOOT and DUAL BOOT

- Configuration

- JTAG configuration

- Offers up to six GowinCONFIG configuration modes - AUTOBOOT, SSPI, MSPI, CPU, SERIAL, DUAL BOOT

Applications

- Communication

- Industrial control

- Consumer (Mobile and wearable)

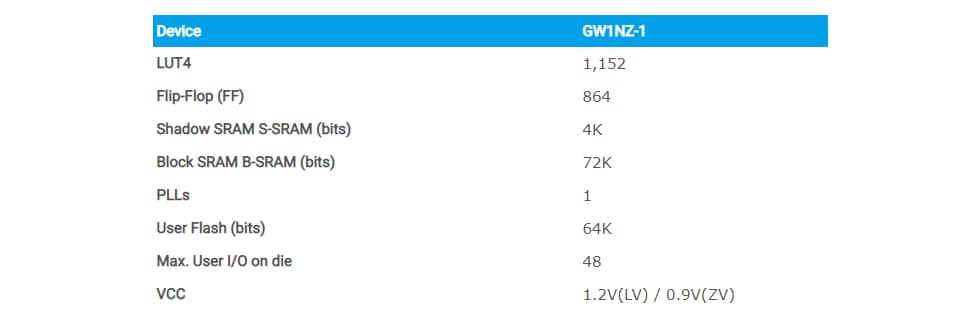

Specifications Chart

Architecture Overview

公開: 2020-07-16

| 更新済み: 2024-09-06