Lattice Semiconductor MachXO3D™ FPGA

Lattice Semiconductor MachXO3D™ FPGAは、次世代の低密度PLDで、強化されたセキュリティ機能とオンチップデュアルブートフラッシュが搭載されています。MachSO3D FPGAは、ハードウェアのRoot-of-Trustおよびデュアルブート機能を用いて、安全な制御アプリケーションを強化します。MachXO3Dは、製品ライフサイクル全体での包括的で柔軟性に富んだ堅牢なハードウェア・セキュリティの実装を簡素化しています。このカスタマイズ可能なアプローチによって、広範なシステムアーキテクチャでの実装が可能になります。MachXO3D FPGAには、暗号を検出して悪意のあるコードから起動を防止するなど、数多くの堅牢なセキュリティ機能があります。オンデバイス構成フラッシュによってデュアルブートが可能になり、外部メモリの必要性が排除されます。強化されたデバイス構成エンジンによって、信頼されたソースからのFPGA構成のみをインストールできるようにします。MachXO3Dは、オンチップ・フラッシュからの柔軟性に富んでおり信頼性が高く安全な構成も実現しており、暗号化および認証オプションが備わっています。

MachXO3Dは、NIST SP 800 193プラットフォーム・ファームウェア耐性(PFR)ガイドラインに準拠しています。MachXO3Dは、超低消費電力(ZC)または高性能(HC)の2つの性能レベルでご用意があります。MachXO3D PLDは、省スペース10 x 10mm QFNから19 x 19mm caBGAにいたるまで、広範な高度ハロゲンフリー・パッケージでご用意があります。MachXO3Dは、同じパッケージ内での密度移行に対応しています。

特徴

- プラットフォームの最初のON、最後のOFFのデバイスにRoot-of-Trustを統合することによって、ハードウェアセキュリティの実装を簡素化

- デバイスの製造と輸送、プラットフォームの製造、設置、操作、廃止をはじめとする、製品ライフサイクル全体でのセキュリティに対応

- データセキュリティ、装置のセキュリティ、データ認証、設計セキュリティ、ブランド保護を実現することによって、さまざまな脅威に対する包括的な保護を実現

- セキュアデュアルブート構成ブロックと組み合わされたプログラマブルロジックによって、設計実装時の柔軟性が実現しており、機器の展開後の安全な更新を保証

- NIST SP 800-193 PFRおよびCAVPガイドラインに準拠した堅牢なセキュリティと事前検証された暗号化機能の提供、不揮発性メモリの保護、悪意のあるコードの検出をし、破損した場合に回復します

アプリケーション

- 安全なブートとRoot of Trust

- 家庭用電子機器

- 計算とストレージ

- ワイヤレス通信

- 産業用制御システム

- 車載システム

MachXO3Dボードを表示

ビデオ

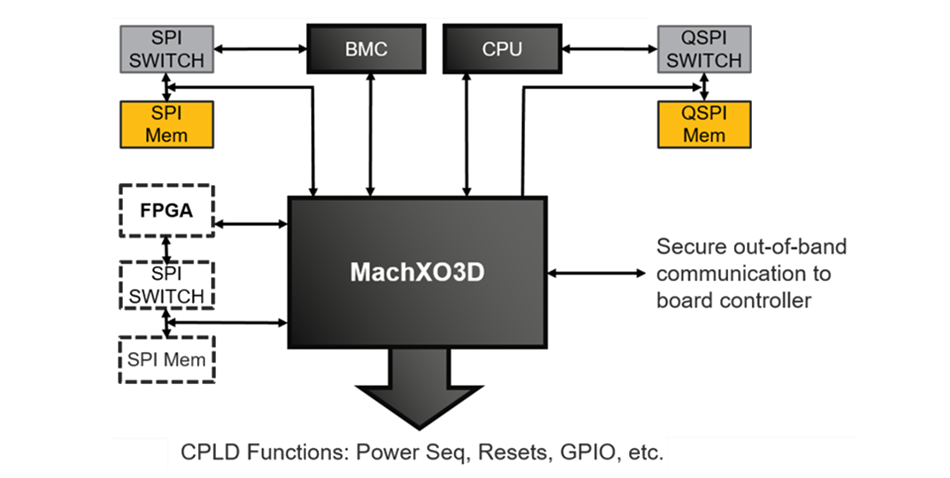

セキュア制御PLDの図

•デュアルブートおよびハードウェアRoot-of-Trustを用いた安全な制御PLD機能の強化

Chain of Trustの図

•システム全体を保護するChain of Trustの最初のリンクであるハードウェアRoot-of-Trust

•電源投入時にMachXO3Dの構成イメージを暗号認証する 強化されたデバイス構成エンジン

•電源投入時に他のプラットフォーム・ファームウェアを認証する暗号化機能を実現している組み込みセキュリティブロック

•インスタントON機能が搭載されているMachXO3Dは、プラットフォームで安全に起動する最初のデバイスであり、Chain of Trustの優れたアンカー

セキュアサーバの図

•MachXO3Dが悪意のある攻撃から自身を保護、検出、回復できる強化された安全な構成ブロック

•複数のプラットフォームファームウェアを同時に保護、検出、回復できる並列処理機能を実現しているFPGAファブリック

•NIST SP 800 193プラットフォーム・ファームウェア耐性(PFR)ガイドラインに準拠