Nexperia 74LVC(H)16373A 16ビットD-Type透明ラッチ

Nexperia 74LVC(H)16373A 16-bit D-Type透明ラッチは、個別のD型入力が特徴で、バス保持((74LVCH16373A専用)が備わっており、各ラッチおよびバス指向アプリケーションを対象とした3ステート出力を目的としています。1つのラッチイネーブル(LE)入力および1つの出力イネーブル(OE)は、各8進数に対して提供されています。これらの入力は、入力が無効の場合に3.3Vまたは5Vデバイスのいずれか一方から駆動でき、最高5.5Vの出力に適用できます。これらの特徴によって、混合3.3Vおよび5Vアプリケーションで使用できるようになります。74LVC(H)16373A 16ビットD-Type透明ラッチには、CMOSテクノロジが組み込まれており、低電力消費とマルチタイプ・フロースルー規格ピン配列アーキテクチャが組み込まれています。これらのデバイスは、3ステートの真の出力が搭載されている2つの8セクションDタイプ・トランスペアレント・ラッチで構成されています。LEがHIGHの場合、Dn入力でのデータはラッチに入ります。この状態においてラッチは透明であり、対応するD入力変化にともなってラッチ出力が変化します。

特徴

- 5Vロジックへのインターフェイス向け5V耐性入力/出力

- 広い電源電圧範囲: 1.2V~3.6V

- CMOS低電力消費

- マルチバイトのフロースルー規格ピン配列アーキテクチャ

- 最小ノイズとグランドバウンスのための複数の低インダクタンス供給ピン

- TTLレベル対応の直接インターフェイス

- すべてのデータ入力には、バスホールド(74LVCH16373A-Q100のみ)あり

- 指定温度範囲: -40°C~85°Cおよび-40°C~125°C

- VCC=0Vの場合に高インピーダンス

- JEDEC標準互換:

- JESD8-7A (1.65V~1.95V)

- JESD8-5A (2.3V~2.7V)

- JESD8-C/JESD36 (2.7V~3.6V)

- ESD保護:

- MIL-STD-883、2000V超過メソッド3015

- 2000V超過HBM JESD22-A114F

- MM JESD22-A115-Aは200V (C=200pF、R=0Ω) 超過

- CDM ANSI/ESDA/Jedec JS-002: 1000V超

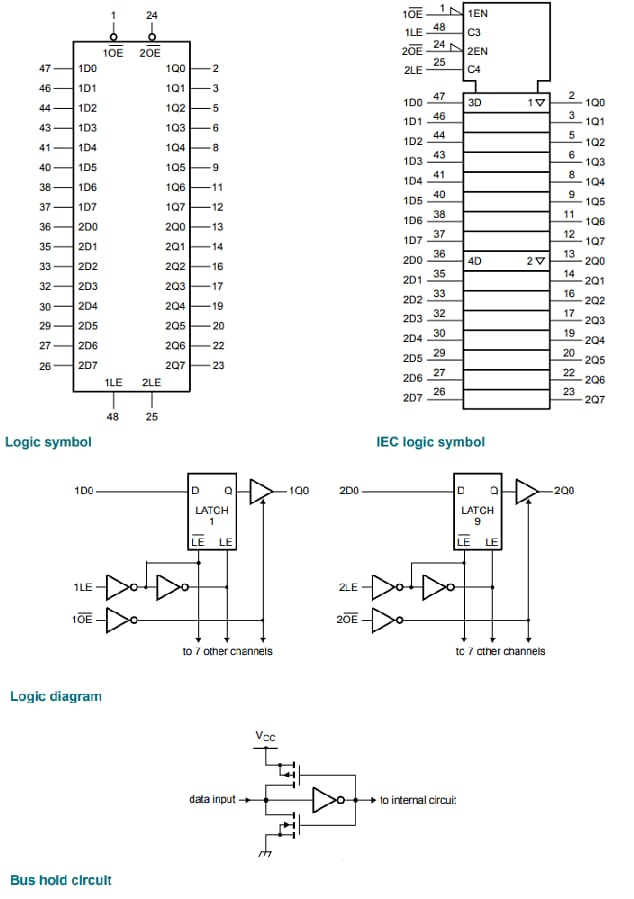

機能図

View Results ( 4 ) Page

| 部品番号 | データシート | 回路数 | 論理タイプ | 論理ファミリ | 出力回線数 | 高レベル出力電流 | 伝搬遅延時間 | 供給電圧 - 最小 | 供給電圧 - 最大 | チャンネル数 | 入力回線数 | パッケージ/ケース |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 74LVCH16373ADGG:11 |  |

2 Circuit | CMOS, TTL | LVCH | 16 Line | - 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | TSSOP-48 |

| 74LVC16373ADGG,118 |  |

2 Circuit | CMOS | LVC | 16 Line | - 24 mA | 12 ns at 1.2 V, 3 ns at 3.3 V | 1.2 V | 3.6 V | 16 Channel | 16 Line | TSSOP-48 |

| 74LVC16373ADGVJ |  |

2 Circuit | CMOS, TTL | LVC | 16 Line | - 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | TVSOP-48 |

| 74LVCH16373ADGVJ |  |

2 Circuit | CMOS, TTL | LVCH | 16 Line | - 24 mA | 6 ns | 1.2 V | 3.6 V | 2 Channel | 16 Input | TVSOP-48 |

公開: 2019-05-27

| 更新済み: 2023-04-26