Texas Instruments AM654x/AM652x ARM™ベースプロセッサ

Texas Instruments AM654x/AM652x ARM™ベースのプロセッサは、最先端のインダストリ4.0組み込み製品の複雑な処理ニーズを満たすように構築されたArm® アプリケーションプロセッサです。AM654xおよびAM652xデバイスには、4つまたは2つのArm® Cortex®-A53コアが組み合わされており、デュアルArm Cortex-R5F MCUサブシステムが搭載されています。これらには、最終製品の機能安全目標の達成に役立つことを目的とした機能があります。また、3つのギガビット産業用通信サブシステム(PRU _ ICSSG)も搭載されており、機能安全アプリケーションを対象とした産業接続と処理が備わった高性能産業用制御が可能なSoCを作成できます。AM65xxは現在、IEC 61508に準拠したTÜV SÜDの認証を取得するための評価を受けています。Cortex-A53の4つのArm AM654xコアは、共有L2メモリが搭載された2つのデュアルコアクラスタに配置されており、2つの処理チャンネルを作成できます。AM652xの2つのArm Cortex-A53コアは、単一のデュアルコアクラスタおよび2つのシングルコアクラスタオプションでご用意があります。信頼性のためにオンチップメモリ、周辺機器、相互接続に豊富なECCが含まれています。全体としてSoCには、機能安全目標を達成できるお客様の設計システムに役立つように設計された機能があります。暗号化アクセラレーションとセキュアブートは、一部のAM654xおよびAM652xデバイスに加えて、DMSCで管理されている詳細なファイアウォールでも使用できます。

Arm Cortex-A53 RISC CPUは、Arm Neon™エクステンションを用いたプログラマビリティを実現しています。デュアルArm Cortex-R5F MCUサブシステムは、2つのコアとして汎用的に使用に利用できます。あるいは、lockstepで使用し、機能安全アプリケーションのニーズを満たす上で役立ちます。PRU _ ICSSGサブシステムを使用して、Profinet IRT、TSN、Ethernet/IP、EtherCAT (その他多数)などの産業用イーサネットの最大6ポートを実現できます。あるいは、標準のギガビット・イーサネット接続に使用できます。

Texas Instrumentsは、プロセッサSDK Linux、Linux-RT、RTOS、Android、Cコンパイラ、ソースコード実行の可視化を目的としたデバッギング・インターフェイスをはじめとするArmコアのための完全セットのソフトウェアと開発ツールを実現しています。該当する機能安全およびセキュリティ文書は、機能安全またはセキュリティ関連システムの開発にお客様を支援するために使用されます。

特徴

- プロセッサ・コア

- 最大1.1GHzでのデュアルまたはクアッドコアArm Cortex-A53マイクロプロセッサ・サブシステム

- 最大2つのデュアルコアまたは2つのシングルコアArm Cortex-A53クラスタ(SECDEDをはじめとする512KB L2キャッシュ搭載)

- 各A53コアには、32KB L1 ICacheおよび32K L1 DCacheあり

- 最大400MHzでのデュアルコアArm Cortex-R5F

- Lockstepモードに対応

- 16KB ICache、16KB DCache、64KB RAM / R5Fコア

- 最大1.1GHzでのデュアルまたはクアッドコアArm Cortex-A53マイクロプロセッサ・サブシステム

- 産業用サブシステム

- 3つのギガビット産業用通信システム(PRU_ICSSG)

- PRU_ICSSGあたり最大2つの10/100/1000イーサネットポート

- 2つのSGMIIポートをサポート

- 10/100Mb PRU-ICSSとの互換性

- PRU_ICSSGあたり24×PWM

- サイクル毎の制御

- 強化されたトリップ制御

- PRU_ICSSGあたり18×シグマデルタ型フィルタ

- 短絡

- 過電流

- PRU_ICSSGに準じた6×マルチプロトコル位置エンコーダ・インターフェイス

- 3つのギガビット産業用通信システム(PRU_ICSSG)

- メモリサブシステム

- 最大2MBのオンチップL3 RAM(SECDED)

- マルチコア共有メモリ・コントローラ(MSMC)

- 最大2MB(2バンク× 1MB)SRAM(SECDED搭載)

- 共有コヒーレントレベル2またはレベル3メモリマッピングSRAM

- 共有コヒーレントレベル3キャッシュ

- 256ビット・プロセッサ・ポート・バスおよび40ビット物理アドレスバス

- プロセッサまたはデバイス・マスタに接続する、コヒーレントで統合された双方向インターフェイス

- L2、L3キャッシュ(事前に温まり、フラッシュ後)

- ピークバインドを用いた帯域幅管理

- 1つのインフラ・マスタ・インターフェイス

- シングル外部メモリマスターインタフェース

- 分散仮想システムをサポート

- 内部DMAエンジン–データ配線装置(DRU)に対応

- ECCエラー保護

- 最大2MB(2バンク× 1MB)SRAM(SECDED搭載)

- DDRサブシステム(DDRSS)

- 最大DDR-1600のDDR4メモリ・タイプをサポート

- 32ビット・データ・バスと7ビット・SECDEDバス

- 8GBの合計アドレス指定可能スペース

- 汎用メモリコントローラ(GPMC)

- SafeTI™半導体コンポーネント

- 機能安全アプリケーションを対象とした設計

- IEC 61508の要件に準じた開発

- SIL-3の体系的な整合性を実現

- MCUセーフティアイランドを対象に、SIL-2のランダム障害整合性要件を達成するための十分な診断が搭載されています。

- 残りのSoCを対象に、SIL-2のランダム障害整合性要件を達成するために十分な診断が搭載されています。

- さらに、適切な安全概念(ソフトウェアによる相互比較など)を考慮したSIL-3アプリケーションの実行を達成するために、十分なアーキテクチャ指標が用意されています。

- 機能安全マニュアルを利用可能

- 安全関連認定

- TÜV SÜD [進行中の認証]によるコンポーネントレベル機能安全認証

- 機能安全性の特徴

- 計算が重要なメモリと内部バス相互接続でのECCまたはパリティ

- ファイアウォールによる干渉からの解放(FFI)

- CPU用の内蔵自己テスト(BIST)、ハイエンドタイマー、オンチップラムス

- 診断用のテストのためのハードウェアエラー注入サポート

- 機能安全関連エラーのキャプチャのためのエラー信号モジュール(ESM)

- 電圧、温度、クロック監視

- 複数のクロック・ドメインでのウィンドウモードおよび非ウィンドウ・ウォッチドッグ・タイマ

- MCUアイランド

- デュアルコアArm Cortex-R5Fマイクロプロセッサ・サブシステムの絶縁

- 独立した電圧、クロック、リセット、専用周辺機器

- SoCの他の部分への内部MCSPI接続

- セキュリティ

- セキュアブートサポート

- ハードウェア強化root-of-trust

- バックアップキー経由でのroot-of-trustの切り替えに対応

- テイクオーバー保護、IP保護、アンチロールバック保護のサポート

- 暗号化アクセラレーション・サポート

- 着信データストリームに基づいてキー素材を自動切替できるセッション認識暗号化エンジン

- 暗号コアをサポート

- AES - 128/192/256ビット・キーサイズ

- 3DES–56/112/168ビット・キーサイズ

- MD5、SHA1

- SHA2 -224/256/384/512

- DRBG真の乱数発生器

- RSA/ECC処理を支援するPKA(公開鍵アクセラレータ)

- DMAサポート

- セキュリティデバッギング

- 安全なソフトウェア制御デバッグ・アクセス

- セキュリティ認識デバッギング

- 信頼できる実行環境(TEE)サポート

- Arm TrustZoneベースのTEE

- 絶縁のための広範なファイアウォール・サポート

- 安全なDMAパスと相互接続

- 安全なウォッチドッグ/タイマ/IPC

- セキュアストレージサポート

- OSPIインターフェイスのオンザフライ暗号化および認証サポート

- パケットベースのハードウェア暗号化エンジンを介したデータ(ペイロード)暗号化/認証のネットワーキング・セキュリティ・サポート

- キーおよびセキュリティ管理のためのセキュリティ・コプロセッサ(DMSC)で、専用のデバイスレベルが備わっており、セキュリティソフトウェアのための相互接続を実現

- セキュアブートサポート

- SoCサービス

- デバイス管理セキュリティコントローラ(DMSC)

- 集中型SoCシステムコントローラ

- 初期ブート、セキュリティ、機能安全性、クロック/リセット/電力管理を始めとするシステムサービスを管理

- アクティブおよび低消費電力モード用の電力管理コントローラ

- メッセージマネージャを介したさまざまな処理ユニットとの通信

- 未使用の周辺機器を最適化するための簡素化されたインターフェイス

- トレーシングとデバッギング機能

- 16個の32ビット汎用タイマ

- 2つのデータ移動および制御ナビゲータサブシステム(NAVSS)

- リングアクセラレータ(RA)

- 統合DMA(UDMA)

- 最大2つのタイマーマネージャ(TM)(各1024タイマ)

- デバイス管理セキュリティコントローラ(DMSC)

- マルチメディア

- ディスプレイサブシステム

- 2つのディスプレイ出力に関連する2つの完全入力マッピング・オーバーレイ・マネージャ

- ポートMIPI DPIパラレル・インターフェイス1台

- 1ポートOLDI

- PowerVR SGX544-MP1 3Dグラフィック処理装置(GPU)

- カメラ・シリアル・インターフェイス(MIPI CSI-2)

- 1つのポートビデオキャプチャ: BT.656/1120(組み込み同期なし)

- ディスプレイサブシステム

- 高速インターフェース

- 以下をサポートしているギガビット・イーサネット(CPSW)インターフェイス1台

- RMII(10/100)またはRGMII(10/100/1000)

- IEEE1588(2008附属書D、附属書E、附属書F)、802.1AS PTP搭載

- オーディオ/ビデオブリッジング(P802.1Qav/D6.0)

- 省電力イーサネット(802.3az)

- ジャンボ・フレーム(2024バイト)

- 第45条MDIO PHY管理

- 2つのPCI-Express(PCIe)revision 3.1サブシステム

- Gen2(5.0GT/s)動作に対応

- 2つの独立した1レーンまたは単一の2レーンポート

- 同時ルート複合およびエンドポイント動作のサポート

- USB 3.1デュアルロールデバイス(DRD)サブシステム

- 強化されたSuperSpeed Gen1ポート1個

- USB 2.0ポート

- 各ポートは、USBホスト、USB周辺機器、またはUSB DRDとして独立して構成可能

- 以下をサポートしているギガビット・イーサネット(CPSW)インターフェイス1台

- 一般的な接続

- 6 ×集積回路間(I2C™)ポート

- 5の構成可能なUART/IrDA/CIRモジュール

- 以下として構成された2つの同時フラッシュ・インターフェイス

- 2つのSDIフラッシュ・インターフェイス

- またはHyperBus™およびOSPI1フラッシュ・インターフェイス

- 2× 12ビットアナログデジタルコンバータ(ADC)

- 最大4Mサンプル/s

- 8個の多重アナログセンサー入力

- 8×マルチチャンネル・シリアル・ペリフェラル・インターフェイス(MCSPI)コントローラ

- 内部接続が備わった2個

- 外部インターフェイス搭載6個

- 汎用I/O(GPIO)ピン

- 制御インターフェイス

- 6つの強化されたハイレゾリューション・パルス幅変調(EHRPWM)モジュール

- エンハンスド入力キャプチャ (ECAP) モジュール

- 3×拡張直交エンコーダ・パルス(EQEP)モジュール

- 車載用インターフェイス

- 2×完全CAN-FDに対応しているモジュラ・コントローラ・エリア・ネットワーク(MCAN)モジュール

- オーディオインターフェイス

- 3つのマルチチャンネルオーディオシリアルポート(MCASP)モジュール

- メディアおよびデータストレージ

- 2つのマルチメディアカードとセキュアデジタル(MMC™/ SD)インターフェイス

- 簡素化された電源管理

- デュアル電圧I/Oを完全にサポートしている簡素化された電力シーケンス

- 統合LDOによって、パワーソリューションの複雑性を低減

- SDインターフェイスの自動電圧遷移の対処を目的とした統合SDIO LDO

- パワーソリューションの複雑性を低減する統合パワーオンリセット(POR)生成

- 機能安全監視用の統合電圧スーパーバイザ

- 高速電源過渡の検出を目的とした統合電源グリッチ検出器

- アナログ/システム統合

- 統合USB VBUS 検出

- DDRリセットのためのフェイルセーフI/O

- バスの競合を回避するためにリセット時に無効化されたすべてのI/Oピン・ドライバ

- デフォルトのI/Oがリセット時に無効にしてシステムの競合を回避

- ダイナミックI/O pinmux構成の変更に対応

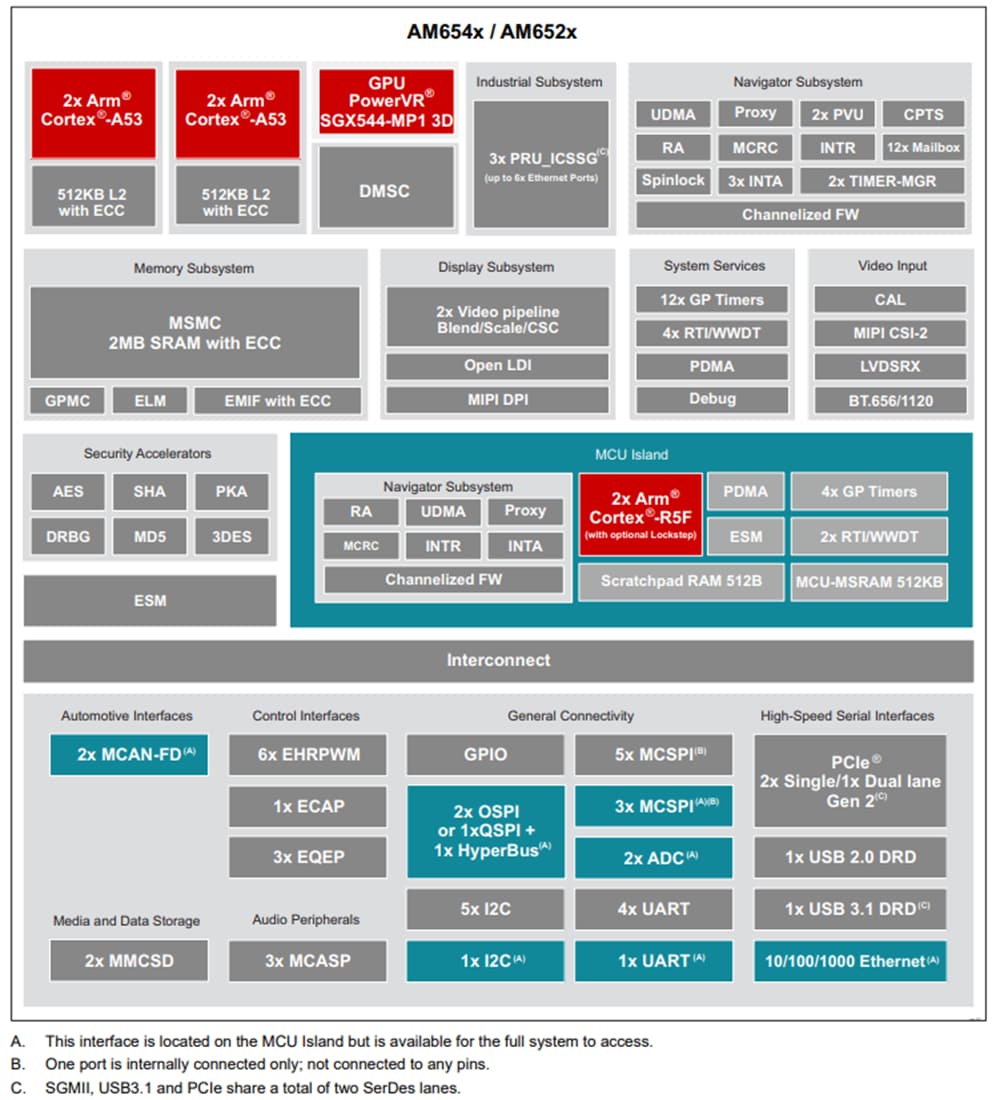

- システムオンチップ(SoC)アーキテクチャ

- UART、I2C、OSPI、HyperBus、パラレルNORフラッシュ、SDまたはeMMC™、USB、PCIe、およびイーサネット・インターフェイスからのプライマリ・ブートをサポート

- 28nm CMOS技術

- 23mm × 23mm、0.8mmピッチ、784ピンFCBGA(ACD)

アプリケーション

- 工業用プログラマブル・ロジック・コントローラ(PLC)

- 安全機能が搭載された工場オートメーション

- マルチプロトコル・フィールドバス通信

- 産業用PC

- 産業ロボット

- ヒューマン・マシン・インターフェイス(HMI)

- グリッドインフラ保護リレー

- ロボティック・モータ・ドライブ

ビデオ

機能ブロック図