Texas Instruments LMK04228超低ノイズクロックジッタクリーナ

Texas Instruments LMK04228超低ノイズクロックジッタクリーナには、高性能およびJEDEC JESD204Bサポートが備わっています。PLL2からの14個のクロック出力を構成すると、7個のJESD204BコンバータあるいはデバイスおよびSYSREFクロックを使用したその他のロジックデバイスを駆動できます。SYSREFは、DCおよびAC結合を使用して実現できます。14個の出力はそれぞれ、従来のクロッキングシステム向けに高性能出力として個別に構成でき、JESD204Bアプリケーションに対する制限はありません。LMK04228超低ノイズクロックジッタクリーナには、電力または性能、デュアルVCO、ホールドオーバー、出力ごとに調整できるアナログおよびデジタル遅延の間でトレードオフできるような高性能と機能が組み合わされています。これによってLMK04228は、柔軟性に富んだ高性能クロッキングツリーの実現に最適です。

特徴

- JEDEC JESD204Bに対応

- 超低RMSジッタ

- 156fs RMSジッタ(12kHz~20MHz)

- 245fs RMSジッタ(100Hz~20MHz)

- –162.5dbc/Hzノイズフロア @ 245.76MHz

- PLL2からの最大14個の差動デバイスクロック

- 最大7個のSYSREFクロック

- 最高クロック出力周波数: 1.25GHz

- PLL2からのLVPECL、LVDSプログラマブル出力

- PLL1からバッファされたVCXOまたはクリスタル出力

- LVPECL、LVDS、2xLVCMOSプログラマブル

- デュアルループPLLatinum™ PLLアーキテクチャ

- PLL1

- 最大3個の冗長入力クロック

- 自動および手動スイッチオーバーモード

- ヒットレス切替とLOS

- 統合低ノイズクリスタル発信器回路

- 入力クロックが失われた際のホールドオーバーモード

- 最大3個の冗長入力クロック

- PLL2

- –224dbc/Hzの正規化された[1Hz] PLLノイズフロア

- 最大155MHzの位相検出器レート

- OSCin周波数ダブラ

- 2個の統合低ノイズVCO

- 50%の負荷サイクル出力デバイス、1~32(奇数と偶数)

- 高精度デジタル遅延

- 25psステップアナログ遅延

- マルチモード:デュアルPLLまたはシングルPLL

- 工業用温度範囲: -40°C~+85°C

- 3.15V~3.45Vでの動作

- パッケージ: 64ピンWQFN(9.0 × 9.0 × 0.8mm)

アプリケーション

- 無線インフラストラクチャ

- データコンバータクロッキング

- ネットワーキング、SONET/SDH、DSLAM

- 医療/ビデオ/軍事/航空宇宙

- テストおよび測定

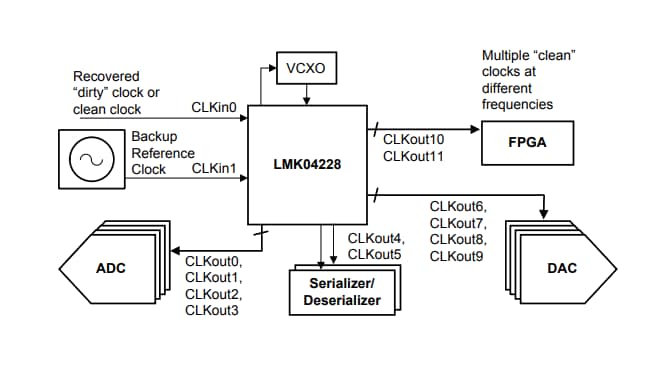

ブロック図

簡略図

公開: 2019-10-14

| 更新済み: 2023-12-11