Texas Instruments LMK5B33216ネットワーク・シンクロナイザおよびジッタ・クリーナ

Texas Instruments LMK5B33216ネットワーク・シンクロナイザおよびジッタ・クリーナは、タイミング精度が < 5ns (D級) のイーサネット・ベースのネットワーキング・アプリケーションの厳しい要件を満たす設計を採用しています。ネットワーク・シンクロナイザは、ヒットレス・スイッチングを実現するために3つのDPLLを内蔵しています。また、ジッタ減衰、プログラミング可能なループ帯域幅があり、外部ループ・フィルタは不要です。この機能により、柔軟性と使いやすさが最大限になります。各DPLLは、対になったAPLLをDPLLリファレンス入力に位相固定します。APLL3は、TI独自のバルク弾性波 (BAW) 技術を採用した超高性能PLLが特長です。DPLLの基準入力周波数にもジッタ特性にも無関係に、42fs (標準値)/60fs (最大値) のRMSジッタで312.5MHzの出力クロックを生成できます。APLL2およびAPLL1には、2番目または3番目の周波数ドメイン、同期ドメインのオプションがあります。リファレンス検証回路は、DPLL基準クロックを監視し、スイッチオーバー・イベントを検出するとクロック間でヒットレス・スイッチングを実行します。ゼロ遅延と位相ビルドアウトを有効にすることで、入力と出力の位相関係を制御できます。このデバイスは、I2CまたはSPIインターフェイスを介して完全にプログラム可能です。オンボードEEPROMを使用してシステムの起動クロックをカスタマイズできます。Texas Instruments LMK5B33216は、フォールバック・オプションとして工場出荷時デフォルトのROM特性も備えています。

特徴

- 超低ジッタBAW VCOベースのイーサネット・クロック

- 標準値42fs/最大値60fsのRMS ジッタ(312.5MHz時)

- 標準値47fs/最大値65fsのRMS ジッタ(156.25MHz時)

- ペアになったアナログ位相ロックループ(APLL)が搭載された高性能デジタル位相ロックループ(DPLL)3個

- DPLLループ帯域幅を1mHz~4kHzにプログラム可能

- 1ppt未満のDCO周波数調整ステップ・サイズ

- 2つの差動入力またはシングルエンドDPLL入力

- 800MHzの入力周波数に対して1Hz(1PPS)

- デジタルホールドオーバーとヒットレス・スイッチング

- 16の差動出力(HSDS/LVPECL、LVDS、HSCL 出力形式をプログラム可能)

- 最大20の合計周波数出力(6つのLVCMOS周波数出力で構成した場合)

- 1Hz (1PPS) ~1250MHzの出力周波数(スイングおよび同相範囲をプログラム可能)

- PCIe Gen 1~6準拠

- I2Cまたは3線式/4線式SPIインターフェイス

アプリケーション

- 有線ネットワーキング

- DC(データセンター)間の相互社外/社内接続

- タイミングカード

- ラインカード

- 固定カード(ピザボックス)

- SyncE(G.8262)、SONET/SDH(Stratum 3/3E、G.813、GR-1244、GR-253)、IEEE 1588 PTP二次クロック

- 56G/112G PAM-4 SerDesのジッタ・クリーニング、ワンダ減衰、リファレンス・クロック発生

- 100G-800Gデータセンタースイッチ、コアルーター、エッジルーター、WLAN

- データセンターおよびエンタープライズコンピューティング

- スマート・ネットワーク・インターフェイス・カード(NIC)

- 光伝送ネットワーク(OTN G.709)

- ブロードバンドの固定ワイヤレスアクセス

- 産業等級

- 試験と計測

- 医療用画像処理

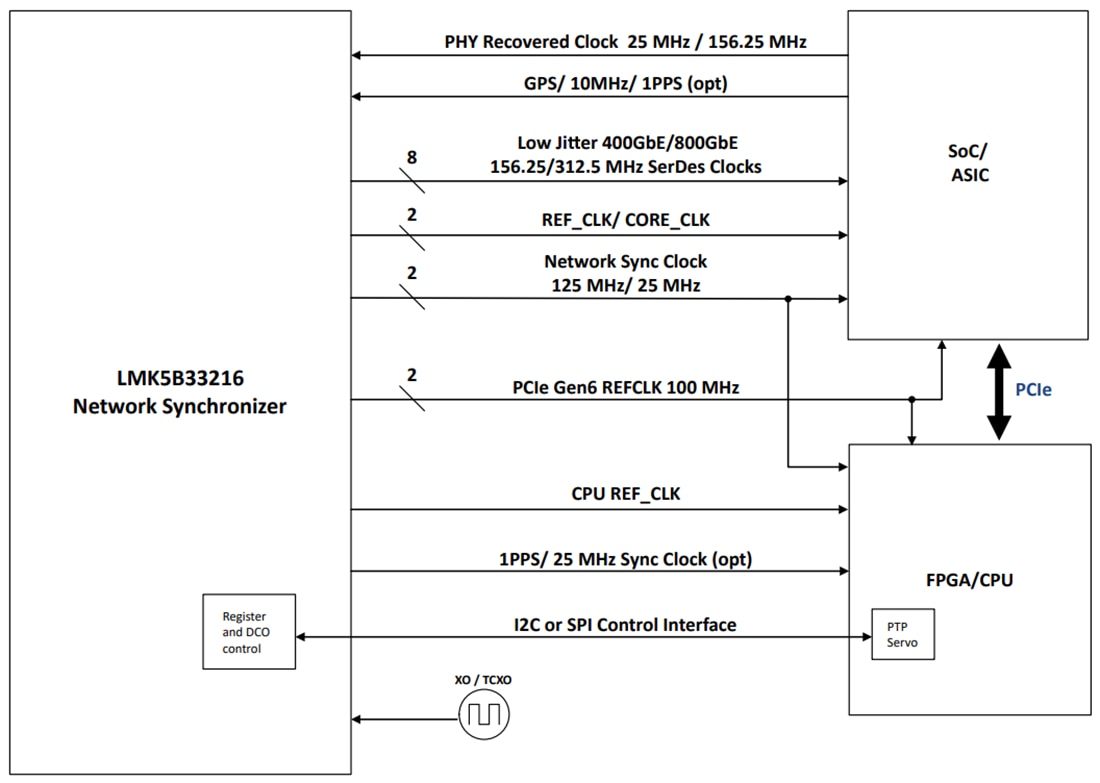

システムブロック図

公開: 2022-09-06

| 更新済み: 2024-01-08