Texas Instruments PCI2050B PCI-to-PCIブリッジ

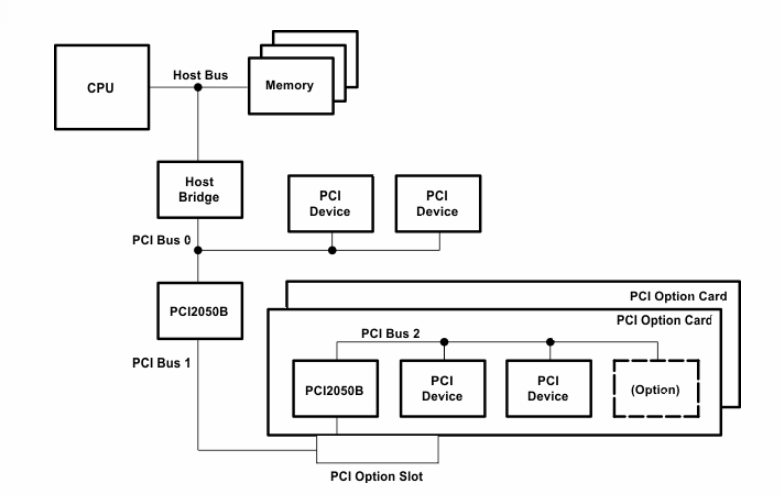

Texas Instruments PCI2050B PCI-to-PCIブリッジは、66MHzの最高バス周波数で動作する2つの周辺部品相互接続(PCI)バス間の性能が高い接続経路が特徴です。一方のマスターともう一方のPCIバスのターゲットの間でトランザクションが発生します。PCI2050Bブリッジを使用すると、両方のバスで同時にトランザクションをブリッジできるようになります。PCI-PCIブリッジは、データスループットを最大化するバーストモード転送をサポートしており、ブリッジを介した2つのバス・トラフィック・パスは独立して動作します。TI PCI2050Bブリッジは、PCIローカルバス仕様に準拠しており、階層バスを作成することによってPCIバスあたりデバイス10台の電気負荷制限、および拡張スロットあたりPCIデバイス1台のの電気負荷制限の克服に使用されます。PCI2050Bは、最大9つの二次バスマスターを対象に2層内部アービターを実現しており、外部バスアービターを使用して実装できます。

CompactPCI™ホットスワップ拡張PCI機能によってPCI2050Bブリッジは、多機能コンパクトPCIカードおよび単一機能カードをホットスワップコンプライアンスへの適合に最適なソリューションです。

特徴

- 2つの32ビット、66MHz PCIバス

- ユニバーサルPCIインターフェイス搭載3.3Vコアロジック(3.3Vおよび5V PCI信号伝達環境との互換性あり)

- 最大9つの二次バスマスターを対象に2層内部アービターを実現しており、外部二次バスアービターをサポート

- 二次PCIクロック出力10個

- 各方向の独立した読取と書込バッファ

- 双方向でのデータスループットを最大化するパイプライン・アーキテクチャを活用したバーストデータ転送

- データスループットの強化を目的とした書込をサポート

- 1つのバスから別のバスへの4つのPCIクロックのフレーム-to-フレーム遅延をサポート

- 両方向で最大3つの遅延トランザクション

- バスロック伝搬

- PCIローカルバス仕様ごとに予測できる遅延

- PCIバス・パワーマネジメント・インターフェイス仕様のためのアーキテクチャ構成

- CompactPCIホットスワップ機能

- リセット中に「低」を駆動する二次バス

- VGA/パレット・メモリーとI/Oデコード・オプション

- 高度サブミクロン、低消費電力CMOS技術

- 208端子PDV、208端子PPM、または257端子MicroStar BGA™パッケージ

ブロック図

公開: 2021-02-03

| 更新済み: 2022-03-11