Texas Instruments TMS320VC5510A固定小数点DSP

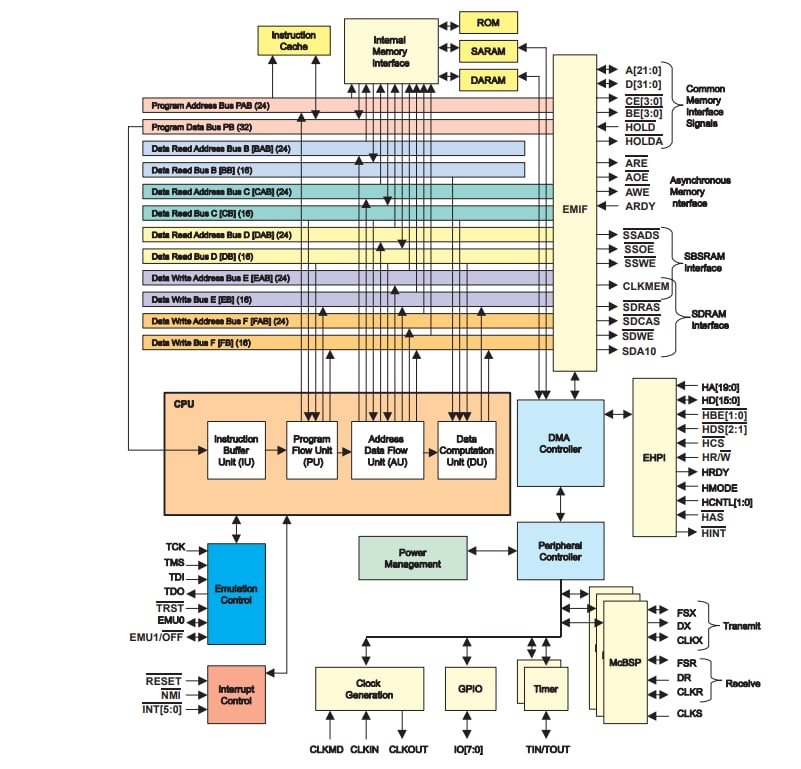

Texas Instruments TMS320VC5510A固定小数点デジタル信号プロセッサは、TMS320C55x DSP世代CPUプロセッサ・コアに基づいています。これらのデバイスは、C55x™DSPアーキテクチャが特徴で、増加した並列性によって高性能および低電力を達成しており、電力損失の低減に焦点を当てています。CPUは、1つのプログラムバス、3つのデータ読取バス、2つのデータ書込バス、周辺機器とDMAアクティビティ専用の追加バスをはじめとする内部バス構造をサポートしています。これらのバスは、単一サイクルで最大3つのデータ読取、および2つのデータ書込を実行できます。同時に、DMAコントローラは、CPUアクティビティに関係なくサイクルごとに最大2つのデータ転送を実行できます。TI TMS320VC5510A C55x CPUは、単一サイクルで17ビットx 17ビットの乗算が可能な2つの積和 (MAC) ユニットを実現しています。追加の16ビットALUは、中央の40ビット算術/論理ユニット(ALU)をサポートします。ALUの使用は、命令セット制御の下で行い、並列アクティビティと電力消費を最適化できます。これらのリソースは、C55x CPUのアドレスユニット(AU)とデータユニット(DU)で管理されています。

TMS320C55x DSPコアは、アプリケーション固有のハードウェアが特定のアルゴリズムで性能を向上できるようにするオープンアーキテクチャで作成されました。拡張機能によってTMS320VC5510Aは、色空間変換、ユーザーインターフェイス動作、セキュリティ、TCP/IP、音声認識、テキスト・ツー・音声変換といった追加機能を実行するために、帯域幅の半分以上で比類のないビデオコーデック性能を発揮できます。

特徴

- 高性能、低電力、固定小数点TMS320C55x™デジタル信号プロセッサ(DSP)

- 6.25/5ns命令サイクル時間

- 160/200MHzクロックレート

- サイクルあたり1つ/2つの命令を実行

- デュアル積演算装置[1秒あたり最大400億回の積和演算(MMACS)]

- 2つの演算/論理ユニット

- 内部プログラムバス1つ

- 3つの内部データ/オペランド読取バス

- 2つの内部データ/オペラント書込バス

- 命令キャッシュ(24Kバイト)

- で構成されている160K x 16ビット対応オンチップRAM

- 4K × 16ビット対応デュアルアクセスRAM (DARAM) (64Kバイト)の8ブロック

- 4K × 16ビット対応シングルアクセスRAM (SARAM) (256Kバイト)の32ブロック

- グルーレス・インターフェイスが搭載されている32ビット外部メモリ・インターフェイス(EMIF)

- 非同期静的RAM(SRAM)

- 非同期EPROM

- 同期DRAM(SDRAM)

- 同期バーストSRAM(SBSRAM)

- 16K × 16ビット対応オンチップROM (32Kバイト)

- 8M × 16ビット最大アドレス指定可能外部メモリスペース

- 6つのデバイス機能ドメインのプログラム可能な低電力制御

- オンチップペリフェラル

- 20ビット対応タイマ2個

- 6チャンネル対応ダイレクトメモリアクセス(DMA)コントローラ

- 3つのマルチチャンネルバッファシリアルポート(McBSP)

- 16ビット並列拡張ホストポート・インターフェイス(EHPI)

- プログラマブルデジタル位相ロックループ(DPLL)クロックジェネレータ

- 汎用I/O(GPIO)ピン8本と専用出力ピン(XF)

- オンチップ・スキャンベースのエミュレーション・ロジック

- IEEE Std 1149.1 (JTAG)バウンダリスキャンロジック

- 240端子MicroStar BGA™; (ボール・グリッド・アレイ) (末尾がGGW)

- 240端子MicroStar BGA™; (ボール・グリッド・アレイ) (末尾がZGW) [無鉛]

- 3.3V I/O電源電圧

- 1.6Vコア電源電圧

アプリケーション

- 圧縮

- ビデオ処理

- 機械ビジョン

- 医療用画像処理

その他のリソース

ブロック図

公開: 2020-10-14

| 更新済み: 2024-09-03